# 2-Cell Supercapacitor Charger with Backup PowerPath Controller

#### **FEATURES**

- 1x/2x Multimode Charge Pump Supercapacitor Charger

- Automatic Cell Balancing

- Ideal Diode Main PowerPath<sup>™</sup> Controller (V<sub>IN</sub> to V<sub>OUT</sub>)

- Internal 2A LDO Backup Supply (CPO to V<sub>OUT</sub>)

- Automatic Main/Backup Switchover

- Input Voltage Range: 2.5V to 5.5V

- Programmable SCAP Charge Voltage

- Programmable Input Current Limit (315mA Max)

- No Load I<sub>VIN</sub> = 55µA (Typical)

- Low Profile, 16-Lead 3mm × 3mm QFN Package

# **APPLICATIONS**

- Smart Power Meters

- Battery-Powered Industrial/Medical Equipment

- 3.3V Solid-State Drives

- Industrial Alarms

- Data Backup Supplies

- Battery Hold-Up Supplies

T, LT, LTC, LTM, Burst Mode, Linear Technology and the Linear logo are registered trademarks and PowerPath is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

# DESCRIPTION

The LTC®3226 is a 2-cell series supercapacitor charger with a backup PowerPath controller. It includes a charge pump supercapacitor charger with programmable output voltage, a low dropout regulator, and a power-fail comparator for switching between normal and backup modes.

The constant input current supercapacitor charger is designed to charge two supercapacitors in series to a resistor-programmable output voltage of 2.5V to 5.3V. The charger input current limit is programmable by an external resistor at up to 315mA.

The internal backup LDO is powered from the supercapacitors and provides up to 2A peak output current with an adjustable output voltage. When the input supply falls below the power-fail threshold, the LTC3226 automatically enters a backup state in which the supercapacitors power the output through the LDO. The input supply power-fail voltage level is programmed by an external resistor divider.

Low input noise, low quiescent current and a compact footprint make the LTC3226 ideally suited for small, battery-powered applications. Internal current limit and thermal shutdown circuitry allow the device to survive a continuous short-circuit from the PROG or CPO pins to ground.

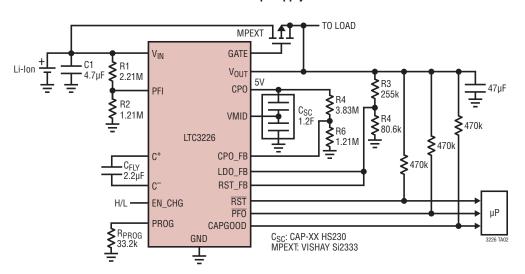

# TYPICAL APPLICATION

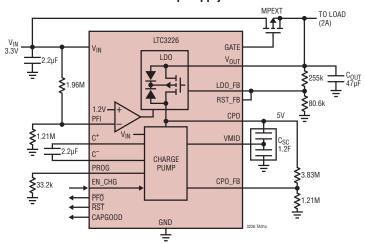

3.3V Backup Supply

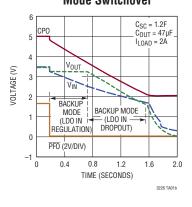

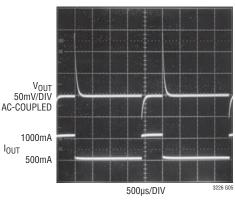

#### Automatic Normal-to-Backup Mode Switchover

3226fa

# **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

V<sub>IN</sub>, V<sub>OUT</sub>, VMID, CPO, RST, PFO, CAPGOOD, LDO\_FB ......-0.3V to 6V EN\_CHG, PFI, RST\_FB, CPO\_FB Voltage.....-0.3V to Max (V<sub>IN</sub>, CPO) + 0.3V Operating Junction Temperature Range (Note 3)....-40 to 125°C Storage Temperature Range ....-65 to 150°C

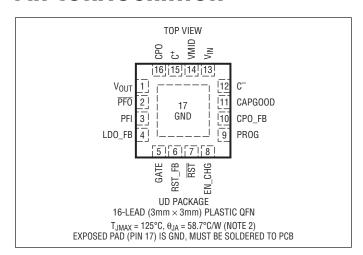

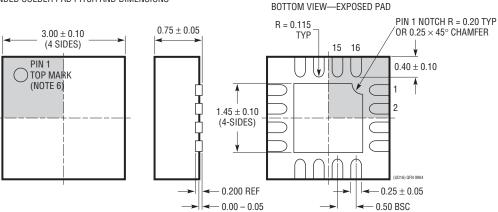

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING* PACKAGE DESCRIPTION TEMPERATURE RANG |                                 | TEMPERATURE RANGE |

|------------------|------------------|----------------------------------------------------|---------------------------------|-------------------|

| LTC3226EUD#PBF   | LTC3226EUD#TRPBF | LFZV                                               | 16-Lead (3mm × 3mm) Plastic QFN | -40°C to 125°C    |

| LTC3226IUD#PBF   | LTC3226IUD#TRPBF | LFZV                                               | 16-Lead (3mm × 3mm) Plastic QFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ (Note 3). $V_{IN} = 3.3V$ , $V_{CPO} = 5V$ , $V_{OUT} = 3.3V$ , VMID = 1/2 $V_{CPO}$ unless otherwise noted.

| SYMBOL                 | PARAMETER                                                                       | CONDITIONS                                                                               |   | MIN  | TYP    | MAX  | UNITS |

|------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---|------|--------|------|-------|

| V <sub>IN</sub>        | Input Supply Range                                                              |                                                                                          | • | 2.5  |        | 5.5  | V     |

| I <sub>VIN(ST)</sub>   | V <sub>IN</sub> Quiescent Current in Normal Mode                                | V <sub>PFI</sub> > 1.2V, V <sub>CPO_FB</sub> > 1.2V, V <sub>IN</sub> < V <sub>CPO</sub>  |   |      | 10     |      | μА    |

| I <sub>CPO(ST)</sub>   | CPO Quiescent Current in Normal Mode                                            | V <sub>PFI</sub> > 1.2V, V <sub>CPO_FB</sub> > 1.2V, V <sub>IN</sub> < V <sub>CPO</sub>  |   |      | 20     |      | μА    |

| I <sub>VOUT(ST)</sub>  | V <sub>OUT</sub> Quiescent Current in Normal Mode                               | $V_{OUT} = V_{IN}, V_{PFI} > 1.2V, V_{CPO\_FB} > 1.2V, V_{IN} < V_{CPO}$                 |   |      | 5      |      | μА    |

| I <sub>CPO(BU)</sub>   | CPO Quiescent Current in Backup Mode                                            | V <sub>PFI</sub> < 1.2V, V <sub>LDO_FB</sub> > 0.8V, V <sub>CPO</sub> > V <sub>OUT</sub> |   |      | 24     |      | μА    |

| I <sub>VOUT(BU)</sub>  | V <sub>OUT</sub> Quiescent Current in Backup Mode                               | $V_{IN} = 0V$ , $V_{PFI} < 1.2V$ , $V_{LDO\_FB} > 0.8V$ , $V_{CPO} > V_{OUT}$            |   |      | 3      |      | μА    |

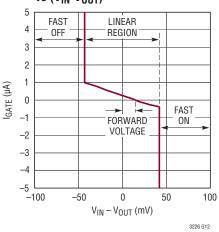

| <b>Ideal Diode</b>     | Controller                                                                      |                                                                                          |   |      |        |      |       |

| V <sub>FWD(EDA)</sub>  | External Ideal Diode Forward Voltage (V <sub>IN</sub> -V <sub>OUT</sub> )       | I <sub>VOUT</sub> = 2mA                                                                  |   |      | 15     |      | mV    |

| V <sub>RTO</sub>       | Fast Turn-Off Voltage (V <sub>IN</sub> -V <sub>OUT</sub> )                      | V <sub>IN</sub> Falling                                                                  |   |      | -45    |      | mV    |

|                        | Fast Turn-On Voltage (V <sub>IN</sub> -V <sub>OUT</sub> )                       | V <sub>OUT</sub> Falling                                                                 |   |      | 45     |      | mV    |

| Charge Pum             | p Supercapacitor Charger                                                        |                                                                                          |   |      |        |      |       |

| V <sub>CPO_FB</sub>    | CPO_FB Pin Threshold for Entering Sleep Mode                                    |                                                                                          | • | 1.18 | 1.21   | 1.24 | V     |

|                        | CPO_FB Pin Hysteresis for Exiting Sleep Mode                                    |                                                                                          |   |      | 20     |      | mV    |

| I <sub>CPO_FB</sub>    | Charge Pump FB Pin Input Leakage                                                | V <sub>CPO_FB</sub> = 1.3V                                                               | • | -50  |        | 50   | nA    |

| f <sub>OSC</sub>       | CLK Frequency                                                                   |                                                                                          |   | 0.75 | 0.9    | 1.05 | MHz   |

| R <sub>0L</sub>        | Effective Open-Loop Output Impedance (Note 4)                                   | $V_{CPO} = 4.5V, C_{FLY} = 1\mu F$                                                       |   |      | 6      |      | Ω     |

| V <sub>PROG</sub>      | PROG Pin Servo Voltage                                                          | V <sub>CPO_FB</sub> < 1.2V                                                               | • | 0.98 | 1.0    | 1.02 | V     |

| I <sub>VIN(ILIM)</sub> | Input Current Limit                                                             | $R_{PROG} = 33.3k, V_{CPO} = 0V$                                                         |   |      | 360    |      | mA    |

| h <sub>PROG</sub>      | Ratio of V <sub>IN</sub> Input Current Limit to PROG Pin<br>Current             | R <sub>PROG</sub> = 33.3k, V <sub>CPO</sub> = 0V                                         |   |      | 10,500 |      | A/A   |

| I <sub>CHRG(1x)</sub>  | CPO Pin Charging Current (1x Mode)                                              | V <sub>IN</sub> = 3.8V, R <sub>PROG</sub> = 33.3k, V <sub>CPO</sub> = 3V                 |   |      | 315    |      | mA    |

| I <sub>CHRG(2x)</sub>  | CPO Pin Charging Current (2x Mode)                                              | $R_{PROG} = 33.3k$                                                                       |   |      | 157.5  |      | mA    |

| I <sub>SC</sub>        | Short-Circuit Charge Current                                                    | PROG Pin Grounded, V <sub>CPO</sub> = 0V                                                 |   |      | 600    |      | mA    |

| V <sub>MODE</sub>      | V <sub>IN</sub> to CPO Voltage Differential for Switching<br>Mode from 1x to 2x |                                                                                          |   |      | 200    |      | mV    |

|                        | 1x/2x Mode Comparator Hysteresis                                                |                                                                                          |   |      | 120    |      | mV    |

| V <sub>CLAMP</sub>     | Maximum Voltage Across Either Supercapacitor<br>After Charging                  |                                                                                          | • |      | 2.65   | 2.75 | V     |

| V <sub>STACK</sub>     | Maximum Supercapacitor Stack Voltage                                            |                                                                                          | • |      | 5.3    | 5.5  | V     |

| VMID                   | VMID Output Voltage                                                             |                                                                                          |   |      | 2.5    |      | V     |

|                        | VMID Current Sourcing Capability                                                | VMID < V <sub>CPO</sub> /2, V <sub>CPO_FB</sub> > 1.24V                                  |   |      | 4.5    |      | mA    |

|                        | VMID Current Sinking Capability                                                 | VMID > V <sub>CPO</sub> /2, V <sub>CPO_FB</sub> > 1.24V                                  |   |      | 5.5    |      | mA    |

|                        | CPO_FB Pin Threshold Voltage (Rising) for CAPGOOD                               |                                                                                          | • | 1.09 | 1.11   | 1.13 | V     |

|                        | CPO_FB Pin Hysteresis for CAPGOOD                                               |                                                                                          |   |      | 20     |      | mV    |

|                        | CAPGOOD Output Low Voltage                                                      | I <sub>SINK</sub> = 5mA                                                                  |   |      | 65     |      | mV    |

|                        | CAPGOOD High Impedance Leakage Current                                          | V <sub>CAPGOOD</sub> = 5V                                                                | • |      |        | 1    | μА    |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 3).  $V_{IN} = 3.3V$ ,  $V_{CPO} = 5V$ ,  $V_{OUT} = 3.3V$ ,  $V_{MID} = 1/2$   $V_{CPO}$  unless otherwise noted.

| SYMBOL                    | PARAMETER                                               | CONDITIONS                   |   | MIN   | ТҮР      | MAX   | UNITS     |

|---------------------------|---------------------------------------------------------|------------------------------|---|-------|----------|-------|-----------|

| LD0                       |                                                         |                              |   |       |          |       |           |

|                           | Minimum CPO Voltage for LDO Operation                   |                              |   | 2.4   |          |       | V         |

| $V_{LDO\_FB}$             | LDO FB Servo Voltage                                    | I <sub>VOUT</sub> = 1mA      | • | 0.76  | 0.8      | 0.82  | V         |

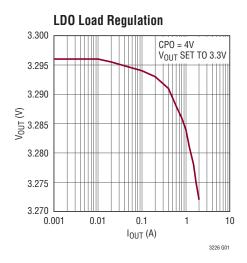

|                           | Load Regulation ΔV <sub>LDO_FB</sub> /ΔI <sub>OUT</sub> | 1mA < I <sub>VOUT</sub> < 2A |   |       | 2.7      |       | mV/A      |

|                           | LDO FET R <sub>DS(ON)</sub>                             | V <sub>CPO</sub> = 3.6V      |   |       | 200      |       | $m\Omega$ |

| I <sub>LDO_FB(LEAK)</sub> | LDO_FB Input Leakage Current                            | $V_{LDO\_FB} = 0.9V$         | • | -60   |          | 60    | nA        |

| I <sub>LIM</sub>          | LDO Current Limit                                       |                              |   | 2     | 4        |       | A         |

| RST_FB, RST               |                                                         |                              |   |       |          |       |           |

| V <sub>RST_FB(TH)</sub>   | RST_FB Threshold (Falling Edge)                         |                              | • | 0.72  | 0.74     | 0.76  | V         |

| V <sub>RST_FB(HYS)</sub>  | RST_FB Hysteresis                                       |                              |   |       | 20       |       | mV        |

| I <sub>RST_FB(LEAK)</sub> | RST_FB Input Leakage Current                            | $V_{RST\_FB} = 0.9V$         | • | -50   |          | 50    | nA        |

|                           | RST Output Low Voltage                                  | I <sub>SINK</sub> = 5mA      |   |       | 65       |       | mV        |

|                           | RST High Impedance Leakage Current                      | $V_{\overline{RST}} = 5V$    | • |       |          | 1     | μA        |

|                           | RST Delay (RST_FB Rising)                               |                              |   |       | 290      |       | ms        |

| Power-Fail Co             | omparator                                               |                              |   |       |          |       |           |

| V <sub>PFI(TH)</sub>      | PFI Input Threshold (Falling Edge)                      |                              | • | 1.175 | 1.2      | 1.225 | V         |

| V <sub>PFI(HYS)</sub>     | PFI input Hysteresis                                    |                              |   |       | 20       |       | mV        |

| I <sub>PFI(LEAK)</sub>    | PFI Input Leakage Current                               | V <sub>PFI</sub> = 0.5V      | • | -50   |          | 50    | nA        |

|                           | PFO Output Low Voltage                                  | I <sub>SINK</sub> = 5mA      |   |       | 65       |       | mV        |

| I <sub>PFO(LEAK</sub> )   | PFO High Impedance Leakage Current                      | V <sub>PFO</sub> = 5V        | • |       |          | 1     | μΑ        |

|                           | PFI Delay to PFO (PFI Falling)                          |                              |   |       | 0.5      |       | μs        |

| EN_CHG                    |                                                         |                              |   |       |          |       |           |

| $V_{IH}$                  | Input High Voltage                                      |                              | • | 1.3   |          |       | V         |

| $V_{IL}$                  | Input Low Voltage                                       |                              | • |       |          | 0.4   | V         |

| I <sub>IH</sub>           | Input High Current                                      |                              | • | -1    |          | 1     | μΑ        |

| I <sub>IL</sub>           | Input Low Current                                       |                              | • | -1    | <u> </u> | 1     | μΑ        |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Failure to solder the exposed backside of the package to the PC board ground plane will result in a thermal resistance much greater than 58.7°C/W.

**Note 3:** The LTC3226 is tested under pulsed load conditions such that  $T_A \approx T_J$ . The LTC3226E is guaranteed to meet specifications from 0°C to 85°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and

correlation with statistical process controls. The LTC3226I is guaranteed over the full –40°C to 125°C operating junction temperature range. The junction temperature,  $T_J$ , is calculated from the ambient temperature,  $T_A$ , and power dissipation,  $P_D$ , according to the formula:

$$T_J = T_A + (P_D \cdot 58.7^{\circ}C/W)$$

Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated thermal package thermal resistance and the environmental factor.

**Note 4:** Output not in regulation;  $R_{OL} = (2 \cdot V_{IN} - V_{CPO})/I_{CPO}$ .

LINEAD TECHNOLOGY

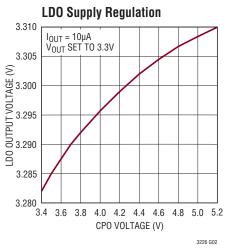

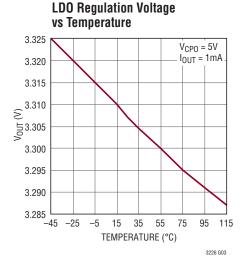

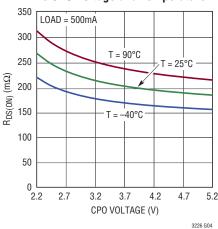

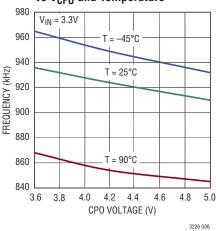

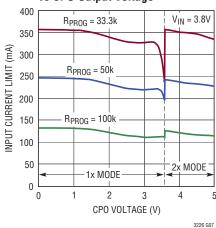

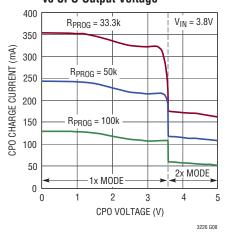

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

LDO FET On-Resistance vs CPO Voltage and Temperature

Charge Pump Input Current vs CPO Output Voltage

Charge Pump Charging Current vs CPO Output Voltage

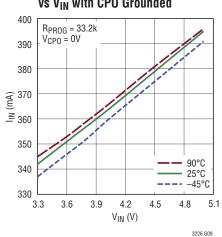

Charge Pump Input Current vs V<sub>IN</sub> with CPO Grounded

3226fa

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , unless otherwise noted.

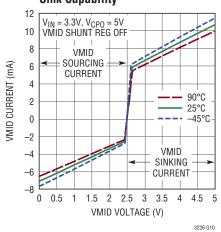

Leakage Balancer Source and Sink Capability

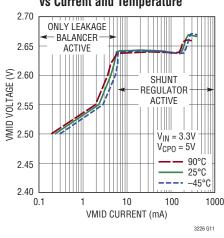

VMID Shunt Regulator Voltage vs Current and Temperature

Ideal Diode Gate Current vs (V<sub>IN</sub>-V<sub>OUT</sub>)

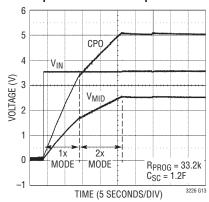

Charge Profile When Top Capacitor = Bottom Capacitor

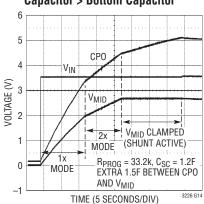

Charge Profile When Top Capacitor > Bottom Capacitor

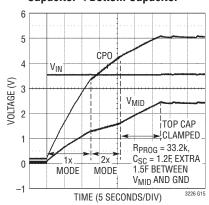

Charge Profile When Top Capacitor < Bottom Capacitor

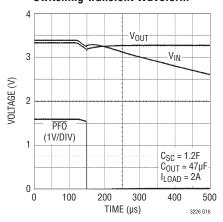

Normal-to-Back-Up Mode Switching Transient Waveform

TECHNOLOGY TECHNOLOGY

# PIN FUNCTIONS

$V_{OUT}$  (Pin 1): Voltage Output. This pin is used to provide power to an external load from either the primary input supply (V<sub>IN</sub>) or the supercapacitor (CPO) if the primary input supply is not available. V<sub>OUT</sub> should be bypassed with a low ESR ceramic capacitor of at least  $47\mu F$  capacitance to GND.

**PFO** (**Pin 2**): Open-Drain Power-Fail Status Output. This pin is pulled to ground by an internal N-channel MOSFET when the PFI input is below 1.2V. Once the PFI input recovers, this pin becomes high impedance.

**PFI (Pin 3):** Power-Fail Input. High impedance input to an accurate comparator with a 1.2V falling threshold and 20mV hysteresis. This pin controls the state of the PFO output pin and the operating mode of the LTC3226.

**LDO\_FB (Pin 4):** Internal LDO Feedback Pin. The voltage on this pin is compared to the internal reference voltage (0.8V) by the error amplifier to keep the output in regulation. An external resistor divider is required between V<sub>OUT</sub>, LDO\_FB and GND to program the LDO output voltage. See the Applications Information section.

**GATE (Pin 5):** External FET Gate Pin. This pin is driven by an internal ideal diode controller to regulate  $V_{OUT}$  to 15mV below  $V_{IN}$ .

**RST\_FB** (**Pin 6**): Reset Comparator Input. High impedance input to an accurate comparator with a 0.74V falling threshold and 20mV hysteresis. This pin controls the state of the RST output pin. An external resistor divider is required between V<sub>OUT</sub>, RST\_FB and GND. It can be the same resistor divider as the LDO\_FB divider. See the Applications Information section.

**RST** (**Pin 7**): Open-Drain Status Output of the RESET Comparator. This pin is pulled to ground by an internal N-channel MOSFET whenever the RST\_FB pin voltage falls below 0.74V. Once the RST\_FB pin voltage recovers, the pin becomes high impedance after a 290ms delay indicating that  $V_{OLIT}$  is within 7.5% of its programmed value.

**EN\_CHG (Pin 8):** Enable Pin for the Charge Pump Supercapacitor Charger with an Internal Pull-Up. Tie this pin to a voltage below 0.4V to disable the internal charge pump.

**PROG (Pin 9):** Charger Input Current Limit Programming Pin. A resistor connected between this pin and GND sets the input current limit for the charger. See the Applications Information section.

**CPO\_FB (Pin 10):** Feedback Pin for the Charge Pump. The voltage on this pin is compared to the internal reference voltage (1.2V) to keep the charge pump output CPO in regulation. An external resistor divider is required between CPO, CPO\_FB and GND to program the CPO output voltage. See the Applications Information section.

**CAPGOOD** (Pin 11): Open-Drain Status Output of the CPO Voltage. This pin is pulled to ground by an internal N-channel MOSFET until CPO\_FB pin reaches 1.11V. Once the CPO\_FB pin exceeds 1.11V, this pin becomes high impedance indicating that the CPO voltage is within 7.5% of its target value.

**C**<sup>-</sup> **(Pin 12):** Internal Charge Pump Flying Capacitor Negative Terminal.

$V_{IN}$  (Pin 13): Primary Input Supply. This pin supplies power to the  $V_{OUT}$  pin through an external P-channel MOSFET and also to the supercapacitors attached to the CPO and VMID pins.  $V_{IN}$  should be bypassed to GND with a low ESR ceramic capacitor of at least 2.2 $\mu$ F depending on the load transient.

VMID (Pin 14): Midpoint of Two Series Supercapacitors.

**C+(Pin15):** Internal Charge Pump Flying Capacitor Positive Terminal. A  $1\mu F$  to  $10\mu F$  X5R or X7R ceramic capacitor should be connected from C+ to C-.

**CPO (Pin 16):** Backup Supply Pin. Connect CPO to the top plate of the top supercapacitor. This pin receives power from  $V_{IN}$  through an internal charge pump doubler and supplies power to  $V_{OUT}$  through an internal LDO when the primary input supply has failed.

**GND** (Exposed Pad Pin 17): Ground. The exposed pad should be connected to a continuous ground plane on the second layer of the printed circuit board by several vias directly under the part to achieve optimal thermal performance.

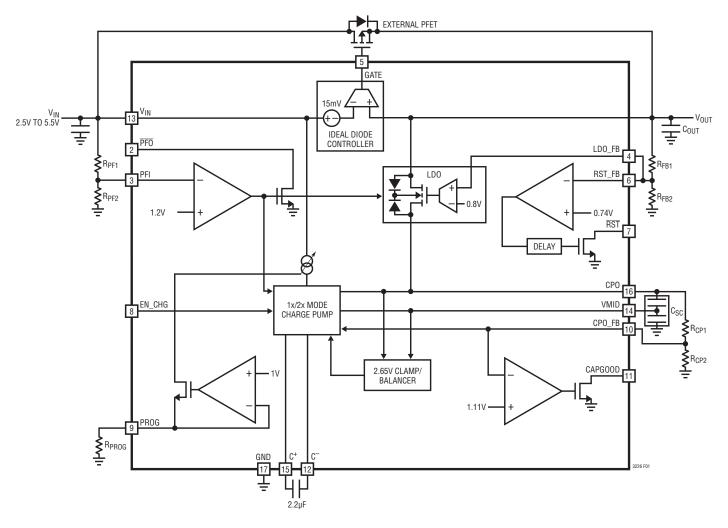

# **BLOCK DIAGRAM**

Figure 1. LTC3226 Block Diagram

# **OPERATION**

The LTC3226 is a 2-cell series supercapacitor charger designed to back up a Li-ion battery or any system rail in the range of 2.5V to 5.3V. It has four principal circuit components: a dual mode (1x/2x) charge pump with an integrated balancer and a voltage clamp, an LDO to supply the load current from the charge stored on the supercapacitor, an ideal diode controller to control the gate of the external FET between  $V_{IN}$  and  $V_{OUT}$ , and a PFI comparator to decide whether to activate the charge pump to charge the supercapacitor stack or to activate the LDO to supply the load when  $V_{IN}$  falls below an externally programmed value.

The LTC3226 has two modes of operation: normal and backup. If  $V_{\text{IN}}$  is above an externally programmable PFI threshold voltage, the part is in normal mode in which power flows from  $V_{\text{IN}}$  to  $V_{\text{OUT}}$  through the external FET and the internal charge pump stays on to top off the supercapacitor stack. If  $V_{\text{IN}}$  is below this PFI threshold, the part is in backup mode. In this mode, the internal charge pump is turned off, the external FET is turned off and the LDO is turned on to supply the load current from the stored charge.

#### **CHARGE PUMP**

One of the principal circuit components of the LTC3226 is a dual mode low noise constant frequency (0.9MHz) regulated charge pump which transfers charge from V<sub>IN</sub> and stores it onto the supercapacitor stack at the CPO pin. The target or termination voltage on the CPO pin is programmed by an external resistor divider using the CPO FB pin. The input current limit to the charger is programmed by an external resistor between the PROG pin and ground. The charge pump turns on when V<sub>IN</sub> exceeds the externally programmable PFI threshold. At the beginning of the charge cycle when the CPO pin voltage is less than  $V_{IN}$ , the charge pump is in 1x mode (linear mode) in which the charge pump acts as a pass element and charges the supercapacitor with a charge current that is limited by the programmed input current limit. As the CPO voltage rises to within 200mV of the input supply voltage, the charge pump switches to 2x mode (doubler mode) in which the average charge current is approximately equal to half the input current limit. As the CPO voltage exceeds the target value by approximately 1%, the charge pump switches turn off and the charge pump enters the sleep mode. In sleep mode, most of the charge pump control circuitry is turned off to minimize quiescent current. As the supercapacitor discharges due to leakage and internal quiescent current load, the CPO pin voltage slowly drops. When the CPO pin voltage drops 1% below the programmed voltage, the charge pump turns on to replenish charge on the supercapacitor and the cycle continues. The charge pump can be turned off by pulling the EN\_CHG pin below 0.4V. However, by default, the charge pump is always enabled via an internal low current pull-up circuit if the EN\_CHG pin is left floating.

#### **Voltage Clamp**

The LTC3226 charge pump is equipped with circuitry to limit the voltage across any supercapacitor in the stack to a maximum allowable preset voltage of 2.65V. If the voltage across the top capacitor (VMID-V<sub>CPO</sub>) ever gets to 2.65V before the CPO pin reaches the target voltage, the charge pump stops charging the top of the stack via the CPO pin, switches to 1x mode and delivers charge directly to the bottom capacitor via the VMID pin until the stack voltage reaches its programmed value. If the voltage across the bottom capacitor reaches 2.65V before the stack gets to its target value, the charge pump continues to deliver charge to the top of the stack via the CPO pin and a shunt regulator turns on to bleed charge off of the bottom capacitor and prevents the VMID pin voltage from rising any further. The shunt regulator is able to shunt the maximum allowable charge current which is approximately 315mA (in 1x mode). In the event both capacitors exceed 2.65V, the charge pump enters sleep mode by turning off most of its circuitry.

#### Leakage Balancer

The LTC3226 is equipped with an internal leakage balancing amplifier which servos the VMID pin voltage to exactly half of the CPO pin voltage. However, it has limited source (~4.5mA) and sink (~5.5mA) capability. It is designed to handle slight mismatch of the supercapacitors due to leakage currents; not to correct any gross mismatch due to defects. The balancer is only active as long as the input supply voltage is above the PFI threshold. The internal balancer eliminates the need for external balancing resistors.

# **OPERATION**

#### **CAPGOOD Status Output**

The LTC3226 charge pump includes a comparator to report the status of the supercapacitors via an open-drain NMOS transistor on the CAPGOOD pin. This pin is pulled to ground until the CPO pin voltage rises to within 7.5% of the programmed value. Once the CPO pin is above this threshold, the CAPGOOD pin goes high impedance.

#### PROG Pin Short-Circuit Protection

Typically the maximum current that the LTC3226 charge pump can deliver is set by the PROG resistor. However, if for any reason, the PROG pin gets shorted to GND, or the user chooses a PROG resistor value which is far smaller than recommended, the charge pump input current is limited to an internally set value of approximately 600mA. Also the maximum current that can be sourced from the PROG pin is limited by an internal resistor to less than 1mA.

#### LOW DROPOUT REGULATOR (LDO)

Another principal circuit component of the LTC3226 is the low dropout regulator (LDO) which transfers power from the supercapacitor stack to  $V_{OUT}$  through a pass element with an  $R_{DS(ON)}$  of approximately  $200m\Omega$ . This LDO has a current limit internally set to 4A. In the event that the input supply voltage falls below the PFI threshold, the PFI comparator promptly turns on the LDO to supply the necessary load without letting the  $V_{OUT}$  rail droop too much. However, to prevent unrestricted current flow from the input to the supercapacitors through the ideal diode, the LDO is turned off until the CPO voltage is greater than  $V_{IN}$  by 100mV typical. The LDO output voltage is programmed through an external resistor divider via the LDO\_FB pin.

#### POWER-FAIL (PFI) COMPARATOR

The LTC3226 contains a fast comparator which switches the part from normal to backup mode in the event the input voltage, V<sub>IN</sub>, falls below an externally programmed

threshold voltage. In backup mode, the charge pump shuts off and the LDO powers the load as long as there is enough charge stored on the supercapacitors. The PFI threshold voltage is programmed by an external resistor divider via the PFI pin. The output of the PFI comparator also drives the gate of an open-drain NMOS to report the status via the PFO pin. In normal mode, the PFO pin is high Impedance but in backup mode, the pin is pulled down to ground.

#### IDEAL DIODE CONTROLLER

The LTC3226 contains an ideal diode controller which controls the gate of an external PFET connected between the input,  $V_{IN}$ , and the output,  $V_{OUT}$ , through the GATE pin. Under normal operating conditions, this external FET constitutes the main power path from input to output. For very light loads, the controller maintains a 15mV delta across the FET between the input and output voltage. In the event  $V_{IN}$  suddenly drops below  $V_{OUT}$ , the controller quickly turns the FET completely off to prevent any reverse conduction from  $V_{OUT}$  back to the input supply.

#### RESET COMPARATOR

The LTC3226 contains a RESET comparator which monitors  $V_{OUT}$  under all operating modes via the RST\_FB pin and reports the status via an open-drain NMOS transistor on the  $\overline{RST}$  pin. At any time, if  $V_{OUT}$  falls 7.5% from its programmed value, it pulls the  $\overline{RST}$  pin low almost instantaneously. However, on the rising edge the comparator waits 290ms after  $V_{OUT}$  crosses the threshold before making the  $\overline{RST}$  pin high impedance.

#### **GLOBAL THERMAL SHUTDOWN**

The LTC3226 includes a global thermal shutdown which shuts down the entire part in the event the die temperature exceeds 152°C. It resumes normal operation once the temperature drops by about 15°C to approximately 137°C.

LINEAR TECHNOLOGY

# APPLICATIONS INFORMATION

# Programming the Supercapacitor Termination Voltage (CPO)

The termination voltage of the supercapacitor stack on the CPO pin can be programmed for any voltage between 2.5V to 5.3V by using a resistor divider from the CPO pin to GND via the CPO FB pin such that:

$$V_{CPO} = V_{CPO\_FB} \bullet \left( 1 + \frac{R_{CP1}}{R_{CP2}} \right)$$

where  $V_{CPO\_FB}$  is 1.2V. See the block diagram in Figure 1. Typical values for  $R_{CP1}$  and  $R_{CP2}$  are in the range of 40k to 5M.

#### **Programming the Input Current Limit for the Charger**

The input current limit for the LTC3226 charge pump is programmed by using a single resistor from the PROG pin to ground. The input current limit is typically 10,500 times the current out of the PROG pin. The PROG pin voltage always servos to 1V as long as the part is not in sleep mode. The program resistor and the input current limit are calculated using the following equations:

$$R_{PROG} = 10,500 \bullet \frac{1V}{I_{VIN(ILIM)}}, \quad I_{VIN(ILIM)} = 10,500 \bullet \frac{1V}{R_{PROG}}$$

where  $I_{VIN(ILIM)}$  is the input current limit for the charge pump charger. The maximum allowable input current limit of 315mA can be achieved by using a PROG resistor of 33.2k. To maximize the charge transfer rate, the charge pump operates in 1x mode when the supercapacitor voltage is less than the input voltage and the charge current out of CPO pin is only limited by the programmed input current limit. However, in 2x mode, the average charge current is approximately half the input current limit.

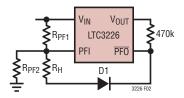

# Programming the Input Voltage Threshold for the Power-Fail Comparator

The input voltage threshold below which the power-fail status pin  $\overline{PFO}$  indicates a power-fail condition and the LTC3226 switches the internal LDO on can be programmed by using a resistor divider from the  $V_{IN}$  pin to GND via the PFI pin such that:

$$V_{IN(PF0\_HI\_L0)} = V_{PFI} \cdot \left(1 + \frac{R_{PF1}}{R_{PF2}}\right)$$

where  $V_{PFI}$  is 1.2V. See Figure 1. Typical values for  $R_{PF1}$  and  $R_{PF2}$  are in the range of 40k to 5M. For a smooth transition from normal to back-up mode, the PFI threshold should be set 50mV to 100mV above the programmed LDO output voltage,  $V_{OUT}$ .

The input voltage above which the power-fail status pin PFO is high impedance and the supercapacitor charger and the ideal diode are enabled is:

$$V_{IN(PF0\_L0\_HI)} = \left(V_{PFI} + V_{PFI(HYS)}\right) \cdot \left(1 + \frac{R_{PF1}}{R_{PF2}}\right)$$

where  $V_{PFI(HYS)}$  is the hysteresis of the PFI comparator. It is internally set to a typical value of 20mV.

The hysteresis can be increased externally by adding a resistor,  $R_H$ , in series with a diode, D1, between the  $\overline{PFO}$  and PFI pins as shown in Figure 2. This network will increase the low-to-high  $V_{IN}$  threshold for  $\overline{PFO}$  while keeping the high-to-low threshold intact. The increase in hysteresis at the input can be calculated as shown:

$$\Delta V_{\text{IN(HYS)}} = \left(V_{\text{PFI}} + V_{\text{PFI(HYS)}} - V_{\text{F}}\right) \bullet \frac{R_{\text{PF1}}}{R_{\text{H}}}$$

# APPLICATIONS INFORMATION

where  $V_F$  is the forward voltage of the diode. As an example, if  $R_{PF1} = 200k$ ,  $R_{PF2} = 120k$ ,  $R_H = 2M$ , and  $V_F = 0.4V$ , the additional hysteresis provided by this network can be calculated using the above equation as follows:

$$\Delta V_{IN(HYS)} = (1.2 + 0.02 - 0.4) V \bullet \frac{200 k\Omega}{2M\Omega} = 82 \text{mV}$$

Figure 2. Increasing PFI Comparator Hysteresis Externally

# Programming the LDO Output Voltage (V<sub>OUT</sub>)

The LDO output voltage in backup mode can be programmed for any voltage between 2.5V to 5.3V by using a resistor divider from the  $V_{OUT}$  pin to GND via the LDO\_FB pin such that:

$$V_{OUT} = V_{LDO\_FB} \bullet \left( 1 + \frac{R_{FB1}}{R_{FB2}} \right)$$

where  $V_{LDO\_FB}$  is 0.8V. See the Block Diagram in Figure 1. Typical values for  $R_{FB1}$  and  $R_{FB2}$  are in the range of 40k to 500k. Too small a resistor will result in a large quiescent current whereas too large a resistor coupled with LDO\_FB pin capacitance will create an additional pole and may cause loop instability.

#### **Programming the Reset Threshold**

The threshold for the reset comparator can be programmed by using a resistor divider from the  $V_{OUT}$  pin to GND via the RST\_FB pin such that:

$$V_{OUT} = V_{RST\_FB} \bullet \left( 1 + \frac{R_{FB1}}{R_{FB2}} \right)$$

where  $V_{RST\_FB}$  is 0.74V. See Figure 1. Typical values for  $R_{FB1}$  and  $R_{FB3}$  are in the range of 40k to 5M. In most applications, the LDO\_FB and RST\_FB pins can be shorted together and only one resistor divider between  $V_{OUT}$  and

GND is needed to set  $V_{OUT}$  and the reset threshold 7.5% below the  $V_{OUT}$  programmed voltage. However, the reset threshold can be set independent of  $V_{OUT}$  by an additional resistor divider.

# Effective Open-Loop Output Resistance ( $R_{0L}$ ) of the Charge Pump

The effective open-loop output resistance ( $R_{OL}$ ) of a charge pump determines the strength of a charge pump. The value of this parameter depends on many factors such as the oscillator frequency ( $f_{OSC}$ ), value of the flying capacitor ( $C_{FLY}$ ), the nonoverlap time, the internal switch resistances ( $R_S$ ), and the ESR of the external capacitors. A first order approximation of  $R_{OL}$  is given below:

$$R_{0L} \cong 2\sum_{S=1\text{to}4} R_S + \frac{1}{f_{0SC} \cdot C_{FLY}}$$

For the LTC3226 charge pump, the sum of the switch resistances is approximately  $2.5\Omega$  in a typical application where  $V_{IN}=3.3V$  and  $V_{CPO}=5V$ . For  $C_{FLY}=1\mu F$  and  $f_{OSC}=1MHz$ , the effective open-loop output resistance of the charge pump can be approximated from the above equation as follows:

$$R_{0L} \cong 2 \cdot 2.5\Omega + \frac{1}{1MHz \cdot 1\mu F} = 6\Omega$$

#### **Maximum Available Charge Current**

In the absence of any internal current limit, the maximum available current out of a charge pump in 2x mode can be calculated from the charge pump input and output voltage and the effective open-loop output resistance  $R_{OL}$  using the following equation:

$$I_{CHRG} = \frac{2V_{IN} - V_{CPO}}{R_{OL}}$$

For example, if the LTC3226 charge pump ( $R_{OL} \cong 6\Omega$ ) has to charge a supercapacitor to 5V from 2.5V input, the charge current available when  $V_{CPO} = 4.8V$  can be calculated as follows:

$$I_{CHRG} = \frac{2 \cdot 2.5 V - 4.8 V}{6 \Omega} = 33.3 \text{mA}$$

/ LINEAR

3226fa

# APPLICATIONS INFORMATION

So even if the charge pump input current limit is programmed for 315mA ( $R_{PROG} = 33.2k$ ), the actual charge current will be considerably less than 157.5mA (half of programmed limit) in 2x mode for very low input supply. For  $V_{IN} = 2.5V$ , the CPO voltage above which the charge current will decrease from the programmed value of 157.5mA ( $R_{PROG} = 33.2k$ ) can be calculated from the previous equation as follows:

$$V_{CPO} = (2 \cdot 2.5V - 157.5mA \cdot 6\Omega) = 4.055V$$

#### **Choosing the LDO Output Capacitor**

In the event  $V_{IN}$  falls below the programmed PFI threshold, the PFI comparator turns off the charge pump and turns on the internal LDO to supply the load from the backed-up supercapacitor storage. However, due to the delay associated with the PFI comparator and LDO circuitry, it could be up to 2µs before the LDO is capable of supplying the load demand at  $V_{OUT}$ . In order to prevent  $V_{OUT}$  from drooping too much during this transition, a  $47\mu F$  ceramic capacitor is recommended at the  $V_{OUT}$  terminal. For any output capacitance,  $C_{OUT}$ , delay,  $\Delta t$ , and load current,  $I_{LOAD}$ , the drop in  $V_{OUT}$ ,  $\Delta V$ , can be calculated using the following equation:

$$I_{LOAD} = C_{OUT} \bullet \frac{\Delta V}{\Delta t}$$

For example, if  $V_{OUT}$  can not tolerate more than 100mV drop under a maximum load of 2A during this transition, the minimum capacitance required at the LDO output can be calculated using the above equation as follows:

$$C_{OUT(MIN)} = 2A \cdot \frac{2\mu s}{100mV} = 40\mu F$$

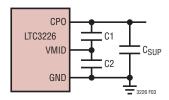

#### **Charging a Single Supercapacitor**

The LTC3226 can also be used to charge a single supercapacitor by connecting two series-connected matched ceramic capacitors with a minimum capacitance of  $100\mu F$  in parallel with the supercapacitor as shown in Figure 3.

#### **Supercapacitor Manufacturers**

Refer to the following table for supercapacitor manufacturers.

**Table 1. Supercapacitor Manufacturers**

| CAP-XX             | www.cap-xx.com            |  |  |

|--------------------|---------------------------|--|--|

| NESS CAP           | www.nesscap.com           |  |  |

| Maxwell            | www.maxwell.com           |  |  |

| Bussmann           | www.cooperbussmann.com    |  |  |

| AVX                | www.avx.com               |  |  |

| Illinois Capacitor | www.illinoiscapacitor.com |  |  |

| Tecate Group       | www.tecategroup.com       |  |  |

|                    |                           |  |  |

Figure 3. Charging a Single Supercapacitor

### **Board Layout Considerations**

Due to high switching frequency and high transient currents produced by the LTC3226 charge pump, careful board layout is necessary for optimum performance. A true ground plane and short connections to all of the external capacitors will improve performance.

Also, to be able to deliver maximum load current from the LDO under all conditions, it is critical that the exposed metal pad on the backside of the QFN package has a good thermal contact to the PC board ground plane. Lack of proper thermal contact can cause the junction temperature to exceed the threshold for thermal shutdown.

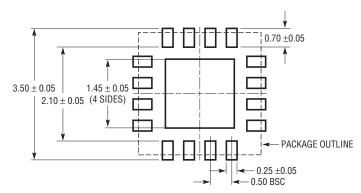

# PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

#### **UD Package** 16-Lead Plastic QFN (3mm × 3mm)

(Reference LTC DWG # 05-08-1691)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

- 1. DRAWING CONFORMS TO JEDEC PACKAGE OUTLINE MO-220 VARIATION (WEED-2) 2. DRAWING NOT TO SCALE

- 2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

TO SERVE AND SCALE FOR COLUMN ATTER

TO SERVE AND SCALE FOR COLUMN ATT

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

# **REVISION HISTORY**

| REV | DATE | DESCRIPTION                                                      | PAGE NUMBER |

|-----|------|------------------------------------------------------------------|-------------|

| Α   | 5/12 | Added Note 3 to operating junction temperature range             | 2           |

|     |      | Modified basic default conditions for Electrical Characteristics | 3, 4        |

|     |      | Modified test conditions for Note 3                              | 4           |

# TYPICAL APPLICATION

#### **Li-Ion Backup Supply**

# **RELATED PARTS**

| PART<br>Number                                                                                                                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | COMMENTS                                                                                                                                                                                                                                                                                                                                   |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LTC3225/<br>LTC3225-1                                                                                                                          | 150mA Supercapacitor Charger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Low Noise, Constant Frequency Charging of Two Series Supercapacitors. Automatic Cell Balancing Prevents Capacitor Overvoltage During Charging. Programmable Charge Current (Up to 150mA). Selectable 2.4V or 2.65V Regulation per Cell (LTC3225), Selectable 2V or 2.25V Regulation per Cell (LTC3225-1). 2mm × 3mm DFN Package            |  |

| Voltage Monitor and Integrated IGBT Drive × 5.8mm × 3mm. Operates from Two AA Batteries, S from 1.8V Up to 10V. No Output Voltage Divider Need |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Integrated IGBT Driver; Voltage Output Monitor; Uses Small Transformers: 5.8mm × 5.8mm × 3mm. Operates from Two AA Batteries, Single Cell Li-Ion or Any Supply from 1.8V Up to 10V. No Output Voltage Divider Needed; No External Schottky Diode Required. Charges Any Size Photoflash Capacitor; 10-Lead (3mm × 3mm) DFN Package          |  |

| LTC3625/<br>LTC3625-1                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                            |  |

| LT3750                                                                                                                                         | Capacitor Charger Controller  Charges Any Size Capacitor; Easily Adjustable Output Voltage. Drives High C NMOS FETs; Primary-Side Sense—No Output Voltage Divider Necessary. Wi Range: 3V to 24V; Drives Gate to V <sub>CC</sub> – 2V. 10-Lead MS Package                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                            |  |

| LT3751                                                                                                                                         | High Voltage Capacitor Charger Controller with Regulation  Charges Any Size Capacitor; Low Noise Output in Voltage Regulation Mode. S Operation Under a No-Load Condition; Integrated 2A MOSFET Gate Driver witl Rail-to-Rail Operation for V <sub>CC</sub> ≤ 8V. Selectable 5.6V or 10.5V Internal Gate Driver Clamp; User-Selectable Over/Undervoltage Detect. Easily Adjustable Output Voltage Sense. Wide Input V <sub>CC</sub> Voltage Rail (5V to 24V). 20-Pin QFN 4mm × 5mm and 20-Lead TSSOP Packages |                                                                                                                                                                                                                                                                                                                                            |  |

| LTC4425                                                                                                                                        | Supercapacitor Charger with Current Limited Ideal Diode                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Constant-Current/Constant-Voltage Linear Charger for 2-cell Series Supercapacitor Stack. V <sub>IN</sub> : Li-Ion/Polymer Battery, a USB Port, or a 2.7V to 5.5V Current-Limited Supply. 2A Charge Current, Auto Cell Balancing, 20µA Quiescent Current, Shutdown Current <2µA. Low Profile 12-Pin 3mm × 3mm DFN or a 12-Lead MSOP Package |  |